# A 2.7pJ/cycle 16MHz SoC with 4.3nW Power-Off ARM Cortex-M0+ Core in 28nm FD-SOI

Guénolé Lallement, Fady Abouzeid, Martin Cochet, Jean-Marc Daveau, Philippe Roche, Jean-Luc Autran

# ▶ To cite this version:

Guénolé Lallement, Fady Abouzeid, Martin Cochet, Jean-Marc Daveau, Philippe Roche, et al.. A 2.7pJ/cycle 16MHz SoC with 4.3nW Power-Off ARM Cortex-M0+ Core in 28nm FD-SOI. ESSCIRC 2017, Sep 2017, Leuven, Belgium. hal-01788172

# HAL Id: hal-01788172 https://amu.hal.science/hal-01788172

Submitted on 8 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A 2.7pJ/cycle 16MHz SoC with 4.3nW Power-Off ARM Cortex-M0+ Core in 28nm FD-SOI

Guénolé Lallement\*†, Fady Abouzeid\*, Martin Cochet<sup>†</sup>\*, Jean-Marc Daveau\*, Philippe Roche\* and Jean-Luc Autran<sup>†</sup>

\*STMicroelectronics, 850 Rue Jean Monnet, F-38926 Crolles Cedex, France.

†IM2NP, Aix-Marseille University and CNRS, UMR7334, Marseille, France.

Email: guenole.lallement@st.com

Abstract—This work presents a System-on-Chip designed for Energy-Harvested applications. It embeds an ARM® Cortex®-M0+ microcontroller, 4 KB RAM, 4 KB ROM, an ultra-low power frequency synthesizer, a custom power switch, and a Power Management Unit enabling Active and Sleep modes. The system fabricated in 28 nm FD-SOI technology achieves 2.7 pJ/cycle at 16 MHz during active mode, and the core consumes 4.3 nW during deep sleep mode. The system operates at a fixed voltage of 0.5 V, and can switch from Active and Sleep/Deep Sleep modes, adjusting the frequency from 16 MHz to 8 MHz or 32 kHz in one cycle upon energy availability. By combining frequency/power switching with extra Reverse Body-Biasing the system power consumption is reduced by 53% and 98% in respectively sleep and deep sleep modes.

#### I. Introduction

Pulsed by the wide variety of low cost, battery-operated and connected applications, Internet-of-Things is considered to be the next decade market with 30.7 billion devices expected in 2020 [1]. Those actual systems' power consumption are in the milliwatt range, hardly sustainable by integrated energy harvesting solutions for autonomous sensor nodes or outdoor monitors [2]. With the advent of new smart objects with perpetual operations, designers and manufacturers must go beyond the Koomey's law which conjectures that the amount of power required for a given computing load will fall by a factor of 2 every 1.5 years. [3]

By enabling efficient low-cost systems, this work aims to push mass market microcontrollers (MCU) down to the microwatts power consumption. The proposed design developed in 28 nm Fully Depleted Silicon-On-Insulator (FD-SOI) technology is based on optimized standard cells and memories in conjunction with design methodology improved for 0.5 V operation with strong tolerance to process variability. The integrated Power Management Unit offers an adaptive power reduction related to the core activity, which helps to achieve 2.7 pJ/cycle ACTIVE and 4.3 nW DEEP SLEEP mode power consumption. This confirms the System-on-Chip's compatibility with power budgets generated by energy-harvesting devices.

In Section II the chosen system architecture and implementation process is presented. The silicon measurements are then presented in Section III. Lastly, an adaptive power reduction analysis is provided based on the core activity in Sec. IV.

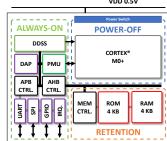

Fig. 1:  $28 \,\mathrm{nm}$  FD-SOI SoC implementation and corresponding block diagram. Active area is  $0.073 \,\mathrm{mm}^2$ .

#### II. SYSTEM ARCHITECTURE AND IMPLEMENTATION

### A. System overview

As presented in Fig. 1, the System-on-Chip (SoC) designed is composed of three Ultra-Low Voltage (ULV) power domains:

- An Always-On (AO) integrating a custom Power Management Unit (PMU), a one-cycle switching frequency synthesizer (DDSS), and event triggered peripherals;

- A Power-Off domain that includes an ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core and a custom power switch;

- A retention domain combining 4 KB of RAM and 4 KB of ROM in the form of 2 SRAM banks.

The PMU was designed as a Finite State Machine to enable ACTIVE and Standby Modes (SLEEP and DEEP SLEEP) at very low power cost. The peripherals included are an UART controller, a SPI interface, 10 GPIO ports, a Wake-up Interrupt Controller and the ARM<sup>®</sup> Debug Access Port. They are memory-mapped to the AHB bus through the APB.

## B. Frequency synthesizer operation

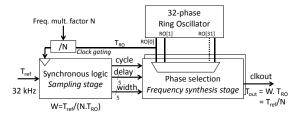

The proposed clock generator (Fig. 2) is a custom alternative to PLL which trades-off phase-locking for lower power and area [4]. It operates on a free-running unregulated internal 32-phases oscillator which period  $T_{RO}$  is compared with a known  $32\,\mathrm{kHz}$  reference via a simple counter. That stage output, W, is then used as the input command of a fractional phase-selection divider, providing output periods with  $1/32^{nd}$  increments. The oscillator is custom designed, while the rest of the circuit is automatically placed and routed from standard cells. The total clock generator area is  $981\,\mathrm{\mu m}^2$ .

Fig. 2: Block diagram the Direct Digital Sampling and Synthesis (DDSS) clock generator [4].

## C. Low energy design considerations

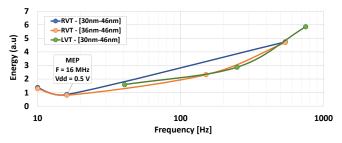

The Cortex®-M0+ minimum active energy operating point (MEP) was extracted using synthesis loops. Various operating conditions and standard cell libraries were explored for  $V_{dd} \in [0.45V;0.9V], \ F \in [1\,\mathrm{MHz};750\,\mathrm{MHz}], \ \mathrm{threshold\text{-}voltage}$   $V_{th} \in [Regular;Low], \ \mathrm{and} \ \mathrm{gate\text{-}length}\ L_g \in [30\,\mathrm{nm};46\,\mathrm{nm}].$  The MEP was achieved at 0.5 V/16 MHz operating condition, using regular threshold-voltage and 34nm to 46nm gate-length standard cell libraries (cf. Fig. 3). Regular-threshold transistors were also selected with regards to the use of Reverse-Body Biasing (RBB) for static power consumption reduction in sleep states.

Fig. 3: Subset of Cortex®-M0+ Synthesis loops results for  $V_{dd} \in [0.45V; 0.9V]$ . Using limited range of gate-lengths and Regular-Threshold Voltage (RVT) standard cell libraries leads to the optimal MEP, with an operating voltage of  $0.5\,\mathrm{V}$  and frequency of  $16\,\mathrm{MHz}$ .

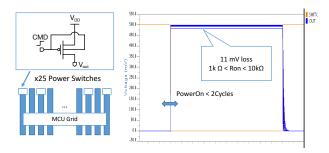

The power switch was strictly designed to minimize the static current consumption. The Cortex®-M0+ was modeled using a current load in the range of 1 µA to 10 µA, corresponding to the simulated current profile of the MCU for a given set of programs. The targeted on-resistance  $(R_{ON})$ was defined with a 10 mV maximum voltage drop target, which induces a limited power impact margin of 2%-4%, that is  $R_{ON} \in [1 \text{ k}\Omega; 10 \text{ k}\Omega]$ . The switch design is based on distributed LVT pMOS transistors with gate tied to the body, offering fast swing recovery and super shut-off performances (Fig. 4). The restoration time was characterized to remove the need for a feedback controller with acknowledgment, replaced by a hard-coded wait operation. These specifications ensure the minimum power consumption overhead due to the controller area and activity power savings, and the inherent switching time when the SoC goes into DEEP SLEEP. (cf. Sec.IV).

The memories used for ROM and RAM are based on 6-transistors bitcells with ultra-low voltage capabilities, enabling operation at 0.5 V and retention at lower supply values. The full system was implemented with ultra-low voltage corners

Fig. 4: Distributed power switches using LVT-transistor design and simulated performances at  $0.5\,\mathrm{V}$ . Total area is  $90\,\mu\mathrm{m}^2$ .

centered at  $0.5\,\mathrm{V}$ , with adjusted clock derating, setup and hold uncertainties. The tolerance to variability was improved by checking the hold timing violations at low voltages, fast/slow process and high/low temperatures.

# III. SILICON MEASUREMENTS

# A. Benchmarking and measured performances

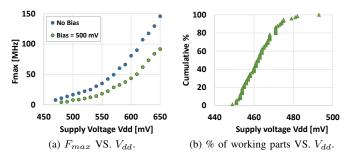

The system was fabricated in 28nm FD-SOI technology, packaged and measured using a custom development board and a Kintex-7 FPGA from Xilinx. A C-code program running the Dhrystone benchmark, SLEEP and DEEP SLEEP operations is used as software for yield measurements on 80 dies at wafer level, and performances measurements on 5 packaged dies, at 25°C. The speed performance obtained are given in Fig. 5a for  $V_{dd} \in [0.45\,\mathrm{V}; 0.65\,\mathrm{V}]$ . The mean clock frequency goes from  $10\,\mathrm{MHz}$  at  $0.47\,\mathrm{V}$  to  $150\,\mathrm{MHz}$  at  $0.65\,\mathrm{V}$  with the targeted  $16\,\mathrm{MHz}$  at  $0.5\,\mathrm{V}$ . The  $F_{max}$  associated to a RBB bias voltage of  $500\,\mathrm{mV}$  is also plotted. Its utilization in SLEEP and DEEP SLEEP modes is scheduled for static power consumption reduction (Sec. IV).

Fig. 5: Measured silicon performances as function of  $V_{dd}$ .

Regarding the yield, the cumulative percentage of working parts from  $0.45\,\mathrm{V}$  to  $0.5\,\mathrm{V}$  is reported in Fig. 5b, as extracted from the wafer. These silicon results show that the reference processor can be supplied down to  $0.48\,\mathrm{V}$ , within a variability window of less than 2%.

# B. Power evaluation

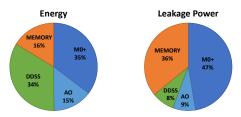

The power contribution of each parts of the system was measured separately at  $0.5\,\mathrm{V}/16\,\mathrm{MHz}$ , plotted in Fig. 6 and the figures associated reported in the first row of Tab. I. The total energy consumption when the system is running is  $2.67\,\mathrm{pJ/cycle}$ . The total power consumption due to the static current is  $1.5\,\mu\mathrm{W}$ , dominated by the M0+ core.

Fig. 6: Pie chart of the energy/cycle (left) and the leakage power (right) SoC's repartition.

# IV. Cortex $^{\circledR}$ M0+ with adaptive power reduction

# A. Available low power modes

The ultra-low power application oriented Cortex®-M0+ processor is a 32-bit ARMv6 architecture with a two-stage pipeline for improved response time and efficiency. Thus, it achieves lower power/higher performances when compared to the previous M0 core [5].

Architecturally, two sleep modes are proposed: normal SLEEP and DEEP SLEEP. In our implementation, the SLEEP behavior is defined by the clock gating of the M0+ core whereas the DEEP SLEEP enables the use of the power switch on the Power-Off domain. Based on these sleep mode features, a PMU was designed and merged with a Wake-up Interrupt Controller (WIC) as additional hardware level to enable mode transitions. With this architecture the SoC user has the opportunity – depending on their application requirements – to clock gate or power down the microcontroller and wake up on certain hardware events.

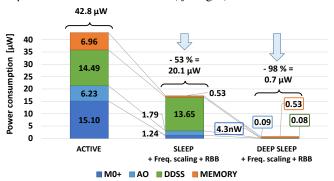

# B. Resulting power savings

Table I demonstrates the leverage offered by the M0+power modes combined with the PMU to reduce power consumption of the system. All measurements were performed at  $0.5\,V/16\,MHz$ . Switching from ACTIVE to SLEEP power mode leads to reduce the core power consumption from  $15.1\,\mu\mathrm{W}$  to  $1.96\,\mu\mathrm{W}$ , reaching its lowest value of  $4.3\,\mathrm{nW}$  in DEEP SLEEP.

TABLE I: ENERGY/CYCLE AND POWER BREAKDOWN

| State      | M0+              | Always-ON | DDSS | Memory | Units |

|------------|------------------|-----------|------|--------|-------|

| ACTIVE     | 0.94             | 0.39      | 0.89 | 0.44   | pJ/c. |

|            | 15.1             | 6.23      | 14.5 | 6.96   | μW    |

| $IDLE^1$   | 0.86             | 0.38      | 0.89 | 0.25   | pJ/c. |

|            | 13.7             | 6.23      | 14.5 | 4.02   | μW    |

| SLEEP      | 0.12             | 0.22      | 0.89 | 0.03   | pJ/c. |

|            | 1.96             | 3.59      | 14.5 | 0.53   | μW    |

| DEEP SLEEP | $2.7e^{-4}$      | 0.21      | 0.89 | 0.03   | pJ/c. |

|            | $4.3\mathrm{nW}$ | 3.49      | 14.5 | 0.54   | μW    |

<sup>&</sup>lt;sup>1</sup> IDLE given as the worst waiting option corresponding to active polling.

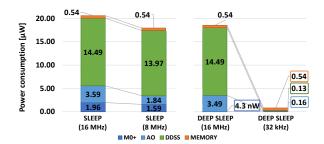

In low power modes, the fastest clock frequency is no longer necessary. Consequently by switching in one cycle the DDSS clock from  $16\,\mathrm{MHz}$  to  $8\,\mathrm{MHz}$  the power consumption of the Always-On (SoC) is reduced by 48% (13%). For further power saving, the DDSS is disabled in DEEP SLEEP and the  $32\,\mathrm{kHz}$  reference clock is used. As reported in Fig. 7 this last technique decreases the AO/SoC power consumption by 95%.

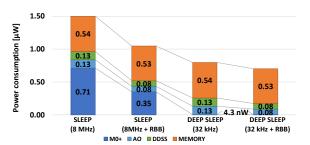

Subsequently, trimming the SoC frequency offers room for Reverse Body-Biasing (RBB) usage leading to a SoC

Fig. 7: Influence of frequency scaling on the power consumption in SLEEP (left) and DEEPSLEEP (right) modes.

static current consumption reduction of 31% and 12.5% in respectively SLEEP and DEEP SLEEP as explained in Fig. 8.

Fig. 8: Reduction of the leakage power using RBB.

By combining together, all these power saving approaches, we induced a power breakdown from ACTIVE to SLEEP with frequency scaling & RBB and DEEP SLEEP with power gating, frequency scaling & RBB of respectively 53% and 98%. This leads to a total power consumption of the SoC of  $0.7\,\mu\text{W}$  in DEEP SLEEP mode (cf. Fig 9).

Fig. 9: Total power breakdown of the SoC.

Lastly, the power modes selected and the associated actions are summarized in Table II.

TABLE II: SUMMARY OF POWER MODES AVAILABLE

| State option   ACTIVE |                  | SLEEP<br>+Freq. scal. +RBB | DEEP SLEEP<br>+Freq. scal. +RBB |  |

|-----------------------|------------------|----------------------------|---------------------------------|--|

| AO clock              | $16\mathrm{MHz}$ | 8 MHz                      | 32 kHz                          |  |

| DDSS                  | ON               | ON                         | OFF                             |  |

| M0+ clock             | $16\mathrm{MHz}$ | Gated                      | Gated                           |  |

| Power switch          | ON               | ON                         | OFF                             |  |

| Body bias             | 0 V              | RBB 0.5 V                  | RBB 0.5 V                       |  |

# C. Adaptive mode selection according to time spent in a mode

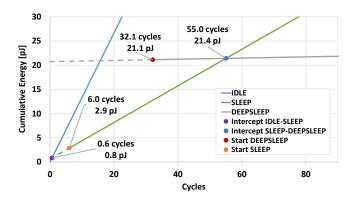

The time required to switch the processor between states results in longer response latency and consume a fair amount of energy. The most energy-efficient SoC inactive state depends of these power and timing penalties. Hence, to select the lowest power mode for a given timeout, it is necessary to evaluate the energy overhead due to these transitions.

Fig. 10: Evolution of the energy consumption in pJ for selected power state.

Fig. 10 gives an insight into power modes switching and the associated figures. Using these performance measurements, the designer can select the best mode according to the SoC activity. The IDLE state is given as the worst power saving mode. It ideally starts in 0 clock cycles and corresponds to an active polling mode of the MCU.

The switching time from ACTIVE to SLEEP or DEEP SLEEP and the associated energy are defined by design. They have been validated using RTL and Prime Time power simulations. This time results in a minimum number of cycle and energy reported in Fig. 10 using the red and orange dots, respectively for SLEEP and DEEP SLEEP modes. The slopes are given by the energy/cycle associated to each mode. Finally, the blue and purple dots define the time when mode switching is beneficial in terms of energy.

Hence, for energy driven applications, the gains of entering the power-off modes is benchmarked: the SLEEP state can directly be selected. Indeed only  $0.6~(\le 1)$  cycle of overhead is reported. However, for sleep time over 55 cycles the DEEP SLEEP should be triggered because it leads to the lowest SoC energy mode.

In the case of duty cycled core operations, the sum of the times spent in ACTIVE mode  $T_{ON}$  and sleep mode  $T_{OFF}$  is constant. Knowing  $T_{ON}$  through a simple counter gives us  $T_{OFF}$  and therefore the best sleep mode can be chosen.

# D. Detailed comparison with the state of the art

The performances of the system is compared with the latest state of the art 32-bit microcontrollers in Table III. This work combines a low power consumption SoC with excellent energy/cycle associated with a PMU allowing efficient dynamic power mode selection.

### V. CONCLUSION

This research presents a System-on-Chip fabricated in 28nm FD-SOI, optimized for energy-harvested applications and offering mass market MCU with very high efficiency:  $2.7\,\mathrm{pJ/cycle}$  at  $0.5\,\mathrm{V/16}\,\mathrm{MHz}$  in ACTIVE mode, and  $4.3\,\mathrm{nW}$  MCU in DEEP SLEEP mode. A frequency synthesizer enabling one-cycle frequency scaling, a dedicated power switch, and a PMU offering efficient mode switching lead to reduce the SoC power consumption down to  $0.7\,\mu\mathrm{W}$ . The system power signatures fit in the energy-harvesting  ${\sim}100\,\mu\mathrm{W}$  power budget, demonstrating autonomous system capabilities [2].

# ACKNOWLEDGEMENTS

The authors would like to thank their colleagues David Bonciani and Janit Kumar, Manohara Mr and Amit Patel for wafer testing and testing board design respectively.

### REFERENCES

- [1] S. Lucero, *IoT platforms : enabling the Internet of Things*. IHS Technology Whitepaper, 2016.

- [2] A. Bahai, "Ultra-low Energy systems: Analog to information," in *European Solid-State Device Research Conference*, vol. 2016-Octob, 2016, pp. 3–6.

- [3] J. G. Koomey *et al.*, "Implications of Historical Trends in the Electrical Eficiency of Computing," *IEEE Annals of the History of Computing*, pp. 2–10, 2011.

- [4] M. Cochet *et al.*, "On-Chip 28nm FD-SOI digital frequency generator for SoC clocking," *Submitted to 2017 IEEE European Solid-State Circuits Conference (ESSCIRC)*, Under review.

- [5] J. Yiu, The Definitive Guide to ARM® Cortex®-M0 and Cortex®-M0+ Processors, 2nd Edition. Academic Press, 2015.

- [6] H. Reyserhove and W. Dehaene, "A 16.07pJ / cycle 31MHz Fully Differential Transmission Gate Logic ARM Cortex M0 core in 40nm CMOS," 2016 IEEE European Solid-State Circuits Conference (ESSCIRC), pp. 257–260, 2016.

- [7] J. Myers et al., "A subthreshold ARM cortex-M0+ subsystem in 65 nm CMOS for WSN applications with 14 Power Domains, 10T SRAM, and integrated voltage regulator," *IEEE Journal of Solid-State Circuits*, pp. 31–44, 2016.

- [8] W. Lim et al., "Batteryless Sub-nW Cortex-M0+ Processor with Dynamic Leakage-Suppression Logic," 2015 IEEE International Solid-State Circuits Conference (ISSCC), pp. 146–148, 2015.

- [9] F. Abouzeid et al., "28nm FD-SOI technology and design platform for sub-10pJ/cycle and SER-immune 32bits processors," 2016 IEEE European Solid-State Circuits Conference (ESS-CIRC), pp. 108–111, 2015.

TABLE III: SUMMARY OF THE ACHIEVE PERFORMANCES AND STATE OF THE ART COMPARISON

| Feature                        | This work        | ESSCIRC'16 [6]     | JSSCC'16 [7]                              | ISSCC'15 [8]                              | ESSCIRC'15 [9]   |

|--------------------------------|------------------|--------------------|-------------------------------------------|-------------------------------------------|------------------|

| Technology                     | 28 nm FDSOI      | 40 nm CMOS         | 65 nm CMOS                                | 180 nm CMOS                               | 28 nm FDSOI      |

| Core                           | ARM® Cortex®-M0+ | ARM® Cortex®-M0    | ARM <sup>®</sup> Cortex <sup>®</sup> -M0+ | ARM <sup>®</sup> Cortex <sup>®</sup> -M0+ | ARM® Cortex®-M4  |

| Memory                         | 4 KB ROM         | $256\mathrm{KB}$   | 2 KB ROM, 16 KB SRAM                      | 256 B                                     | 16 KB            |

|                                | 4 KB SRAM        | 4 KB SRAM          | 8 KB ULV SRAM                             | 250 B                                     | SRAM             |

| Total Area [mm <sup>2</sup> ]  | 0.073            | 2.55               | 3.76                                      | 2.04                                      | 0.15             |

| $V_{dd,MEP}$                   | $0.5\mathrm{V}$  | $0.44{ m V}$       | $0.39\mathrm{V}$                          | $0.55\mathrm{V}$                          | $0.5\mathrm{V}$  |

| F <sub>max</sub> @MEP          | $16\mathrm{MHz}$ | $31.2\mathrm{MHz}$ | 688 kHz                                   | $7\mathrm{Hz}$                            | $45\mathrm{MHz}$ |

| DEEP SLEEP power               | $4.3\mathrm{nW}$ |                    | _                                         | _                                         | _                |

| E/Cycle @E [p]]                | 0.94 (core)      | 16.07 (core)       | _                                         | _                                         | _                |

| E/Cycle @F <sub>max</sub> [pJ] | 2.67 (total)     | 100.34 (total)     | 11.7 (total)                              | 92.04 (total)                             | 8.9 (total)      |